在當今數據驅動的時代,數據已成為企業最寶貴的資產之一。如果數據雜亂無章、定義不清,那么它的價值將大打折扣,甚至可能誤導決策。這正是數據標準登場的時刻。本文將深入淺出地解析數據標準的定義、重要性,并系統地闡述如何建設與管理一套行之有效的數據標準體系,從而為高效、可靠的數據處理奠定堅實基礎。

一、什么是數據標準?

數據標準可以理解為數據的“法律”與“通用語言”。它是一套由管理層面發布、經各方協商一致制定的,關于數據定義、格式、值域、質量、安全以及管理流程的規范性文檔。其核心目的是確保組織內外部對數據的理解、使用和交換是一致、準確且高效的。

簡單來說,它回答了關于數據的幾個基本問題:

- 這是什么數據?(例如,“客戶姓名”這個字段到底指代什么?是身份證姓名、昵稱還是公司注冊名?)

- 數據長什么樣?(例如,日期是“YYYY-MM-DD”格式還是“MM/DD/YYYY”?手機號是否包含國家代碼?)

- 數據從哪里來,誰負責?(明確數據源頭和責任主體)

- 數據的質量要求是什么?(例如,完整性、準確性、唯一性的標準)

- 數據如何使用和共享?(涉及安全分類和訪問權限)

沒有統一的數據標準,不同部門對“客戶”、“訂單”、“收入”等關鍵概念的理解可能千差萬別,導致報表無法對齊、系統難以集成、分析結論矛盾,形成一個個“數據孤島”。

二、為什么數據標準如此重要?

- 提升數據質量與一致性:從源頭統一規范,減少歧義和錯誤,保證“一處定義,處處一致”。

- 打破數據孤島,促進共享:為跨部門、跨系統的數據交換與整合提供通用“字典”,實現數據互聯互通。

- 支撐數據分析與決策:干凈、一致的數據是精準分析和數據智能(如AI/ML)的燃料,直接影響決策的可靠性。

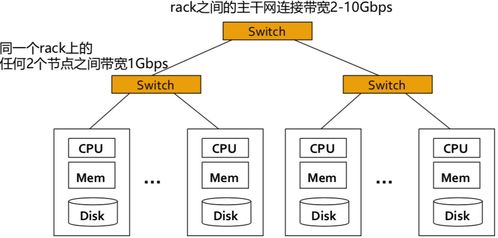

- 提高IT開發與集成效率:標準化的數據模型和接口能大幅降低系統開發、對接和維護的成本與復雜性。

- 滿足合規與審計要求:在數據安全法、個人信息保護法等法規日益嚴格的背景下,標準化的數據管理是合規的基石。

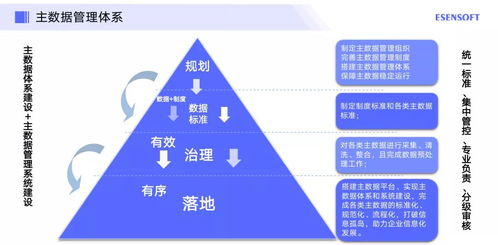

三、如何建設數據標準?—— 一套系統化方法

數據標準建設并非一蹴而就,而是一個需要精心規劃、分步實施的系統性工程。

步驟一:戰略規劃與組織保障

- 明確目標與范圍:確定數據標準項目的業務驅動因素(如支撐數字化轉型、滿足合規),并界定優先實施的范圍(如先聚焦客戶、產品等核心主數據)。

- 建立治理組織:成立由高層領導的數據治理委員會,下設數據標準工作組,明確業務部門(數據所有者)、IT部門(技術支持)和數據管理團隊(專業執行)的職責。

步驟二:現狀評估與需求梳理

- 盤點現有數據資產:梳理業務系統、報表、接口中的數據,識別關鍵數據實體和屬性。

- 分析差異與問題:對比不同來源對同一數據的定義、格式和使用情況,找出不一致、不規范的痛點。

- 調研業務需求:與各業務部門溝通,了解他們對數據的業務定義和使用期望。

步驟三:標準設計與制定

這是核心環節,需為每項數據標準定義清晰的內容,通常包括:

- 標準名稱與標識:唯一標識符。

- 業務定義與描述:用業務語言清晰說明數據的含義和用途。

- 數據類型與格式:如文本、數字、日期,以及具體的長度、精度、顯示格式(如金額保留兩位小數)。

- 參考值域/代碼:明確允許的取值范圍或代碼列表(如性別代碼:1-男,2-女)。

- 數據源與責任方:指明權威數據來源和負責維護的業務部門(數據所有者)。

- 質量規則:定義完整性、準確性、及時性等具體要求。

- 安全與隱私等級:根據敏感程度進行分類,規定訪問和使用權限。

步驟四:評審、發布與宣貫

- 組織跨部門評審:確保標準被各方理解和認可。

- 正式發布:通過制度文件或數據標準管理平臺正式發布,使其具備管理效力。

- 全面宣貫與培訓:讓所有相關的數據生產者、使用者和管理者都了解并掌握新標準。

四、如何管理數據標準?—— 讓標準“活”起來

制定標準只是開始,持續有效的管理才是成敗關鍵。管理核心在于 “治理” 與 “技術” 雙輪驅動。

1. 治理層面:建立長效管理機制

- 生命周期管理:建立標準的申請、變更、廢止流程,確保其能隨業務發展而演進。

- 明確職責與考核:將數據標準執行情況納入相關部門和人員的績效考核。

- 持續監控與審計:定期檢查數據對標情況,發布合規報告。

- 文化建設:通過宣傳、培訓、最佳實踐分享,培養全員的數據標準意識。

2. 技術層面:提供落地支撐工具

- 建設數據標準管理平臺:作為標準的“唯一發布源”和“查詢字典”,集中管理所有標準文檔,并提供便捷的檢索和訂閱功能。

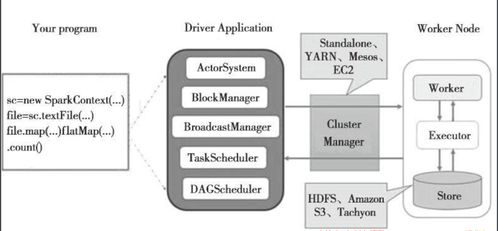

- 與數據處理流程融合(關鍵!):

- 設計時管控:在新建數據模型、數據庫表或API接口時,強制或推薦引用已定義的數據標準。

- 加工時稽核:在ETL(抽取、轉換、加載)或數據開發過程中,嵌入標準校驗規則,對不符合標準的數據進行清洗、轉換或告警。

- 運行時監控:利用數據質量工具,持續監控生產數據是否符合標準,并生成質量報告。

- 消費時解讀:在BI報表、數據門戶中,為字段提供基于標準定義的業務術語解釋,避免誤解。

五、數據處理的核心基石

數據標準是數據治理的“排頭兵”,也是高質量數據處理的核心基石。它連接了業務與IT,統一了數據的“語言”。建設與管理數據標準,是一個從業務戰略出發,通過科學的流程制定規范,并依靠治理組織和技術工具確保其全面落地的持續過程。

對于任何希望從數據中挖掘真正價值、實現智能化運營的組織而言,投資于數據標準體系建設,絕非一項可選的IT項目,而是一項至關重要的戰略性基礎工程。只有打好這個基礎,后續的數據集成、分析、應用和創新才能行穩致遠,讓數據真正成為驅動企業發展的強大引擎。